S1用の拡張メモリを作る

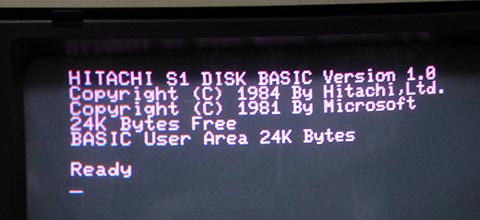

S1は1MBのメモリ空間を利用できることで話題になりましたが、標準搭載されているDRAMの容量は96KB。このうちグラフィックVRAMに48KB使用するのでメインメモリとしては48KB。さらにBASICのワークエリアなどを除くとユーザが使用できるメモリは24KB(DISK BASIC使用時)しかないことになります。この容量はなかり少なかったようで、市販のソフトもメモリ増設が必須のものが多かったように思います。64Kbit DRAMを開発した日立なんだからもうちょっと奮発して欲しかったところですね。

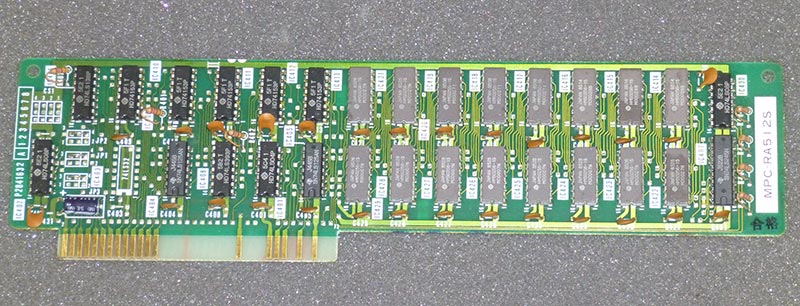

下の写真は、512KB搭載した拡張RAMカードMPC-RA512Sです。当時、市場に出て間もない256Kbit DRAMを16個載せています。はたしてお値段はいくらだったのでしょうか。10万円近くしたのかなぁ。

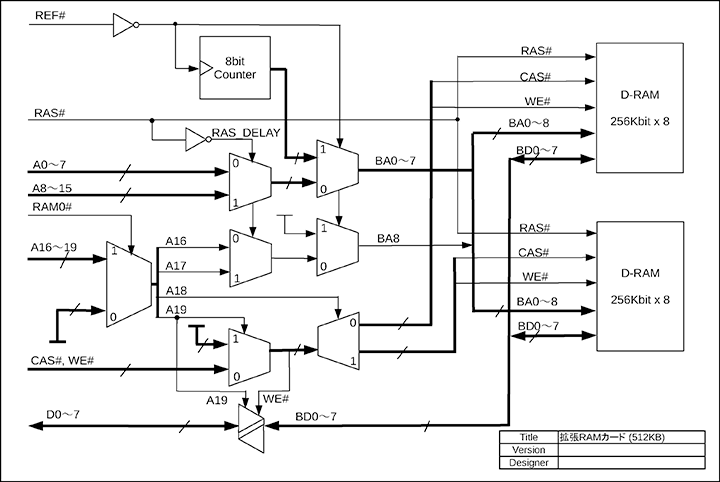

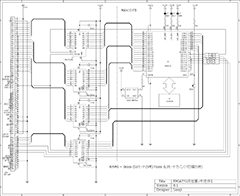

上記拡張RAMカードのブロック図を以下に示しました。ブロック図を見ると本体側からのRAS信号をもとにメモリアドレスをDRAM用のアドレスに変換していることがわかります。

拡張メモリカードの構造が分かったのでさっそくFPGAを実装していきましょう。まずはFPGA内部の実装を考えていきます。今回はMAX10-FB基板にあるSDRAMを使用します。機能としては…

- SDRAMへのアクセスは付属しているSDRAMコントローラを使用する。ただし、SDRAMリフレッシュとS1からのアクセスタイミングが重ならないように修正を加える。S1からのREF信号はSDRAMのタイミングと異なるので使用しない。

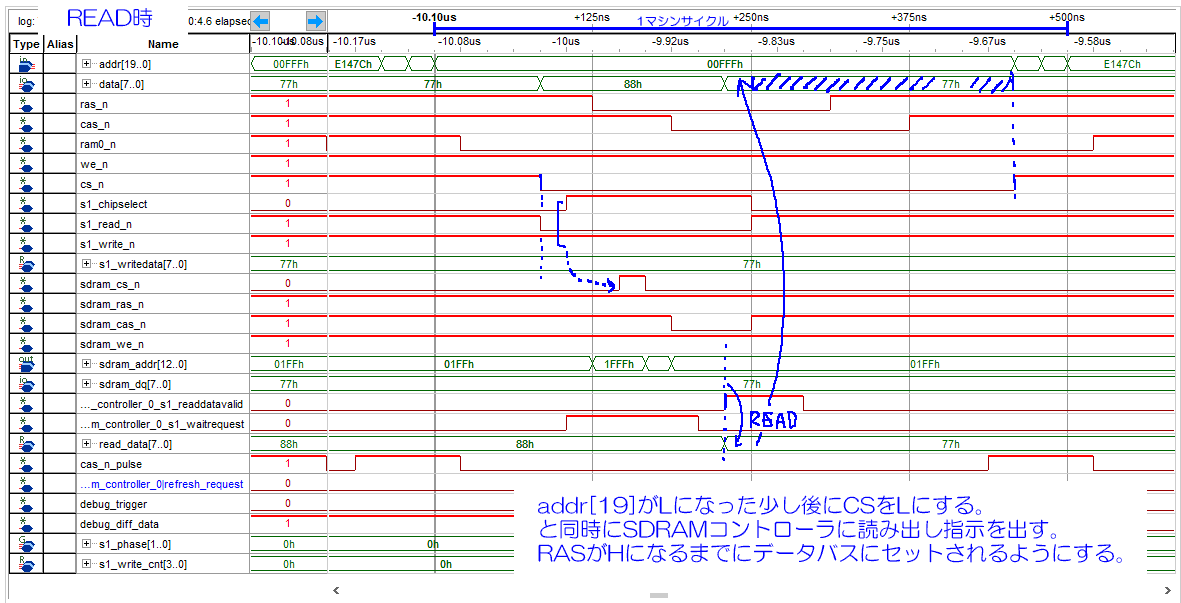

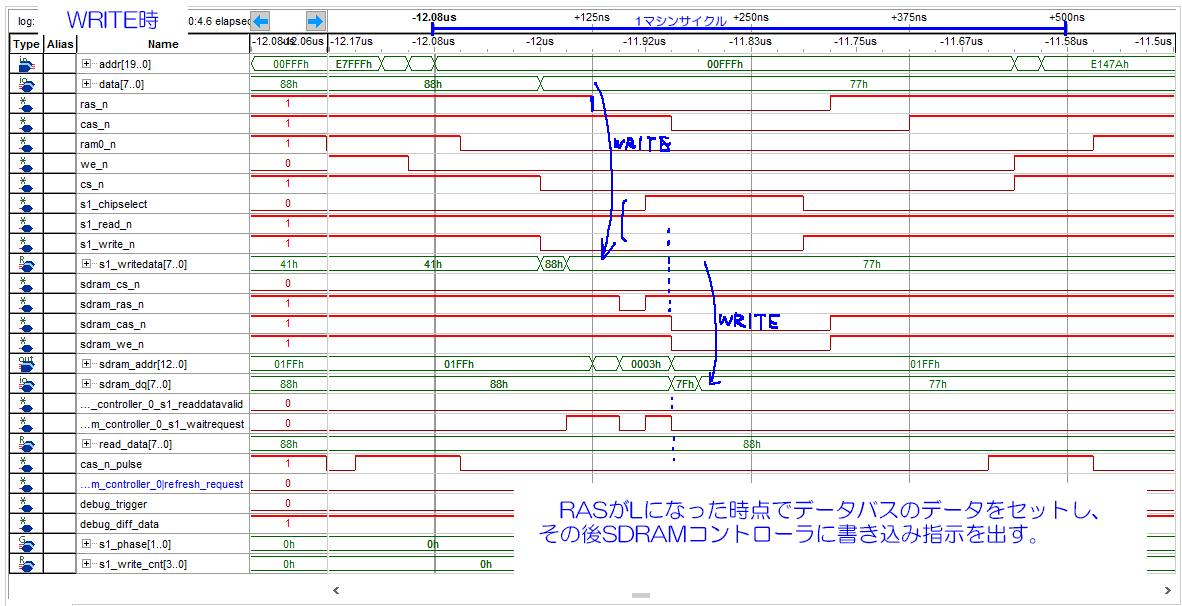

- S1からのRAS,CAS信号を直接SDRAMに渡すことはできないので、RAS信号がLになった時点でアドレスを読んでSDRAMにコマンドを送る。

- SDRAMにコマンド送ってからデータが返るまで最大で24サイクルほどかかる。これを250ns以内で行うためSDRAMは96MHzで動かす。

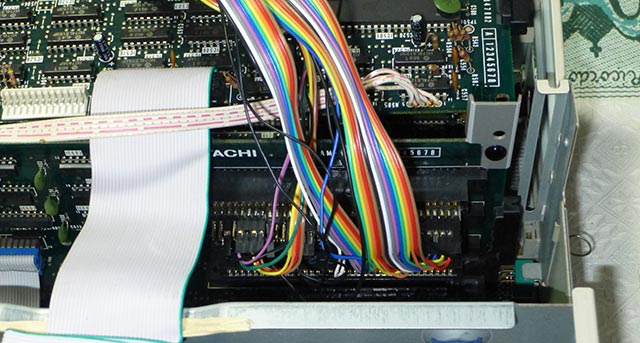

次に、FPGA周りの回路を設計します。今回はアドレスバス20本をすべて見る必要があるためロジックICを追加しています。今回使用したLCX541は基本的にLCX244と同じですがピン配置が異なります。LCX541はピンが揃っているのに対しLCX244はピンが千鳥配置なので使いにくいところがあるんですよね。

ではS1の電源を入れてみます。…メモリとして認識しません。ロジアナで波形を見るとアドレスバスが不安定な状態があります。もしかして接触不良か!?

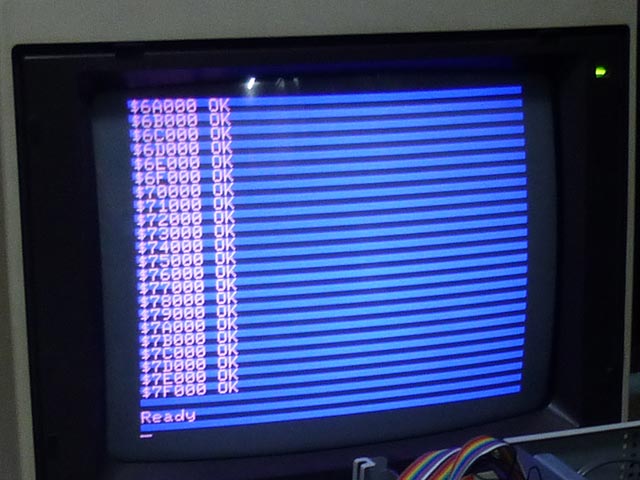

配線をチェックして、もういちど電源ON。…認識しない。やはりタイミングに問題がありそうですね。ロジアナの波形をしばらく眺めていると問題が見えてきました。SDRAMからデータがくる時間が予想より遅くなることがあり、RAS信号の立ち上がりまでにデータが返らない。これがメモリREADに失敗していることになります。このことから以下のように修正することにしました。

- SDRAMアクセスクロックを96→120MHzにあげる。

- SDRAMにコマンドを送るのは、アドレスバスの最上位が0になった時点から開始し、RAS信号がHになるまでにデータを返すようにする。

- データはCAS信号がHになっても出し続けるようにCS信号の長さを調整する。

これをもとにいろいろ試行錯誤した結果、なんとか認識するようになりました。

ちなみに、タイミングチャートは以下のようになります。

まとめ

今回は、S1側からメモリにアクセスするタイミングを勘違いしていた、SDRAMからデータが返るサイクルの長さが予想より遅いなど、このあたりを修正するのに苦労しました。まだ、たまにデータが化けてしまうことがあるというメモリとしては致命的な問題があるのでさらなる調整が必要ですが、とりあえずこれぐらいにしておきます。(おわり)

ソースコード・ダウンロード

s1exmem_010_source.zip (122KB)

[MD5:c0cdaf42fd40b248e9199b5a2d76f42b]

※試される方は自己責任でお願いします。

◆関連ページ◆