マーク5用の拡張メモリを作る

マーク5は日立が開発した64KBのDRAMを標準搭載しています。さらに64KBを拡張できますので今回はこれを実装していきます。RAM拡張端子の各信号についてはこちらを参照ください。なお、これはマーク5専用で元祖レベル3やマーク2とは異なりますのでご注意を。

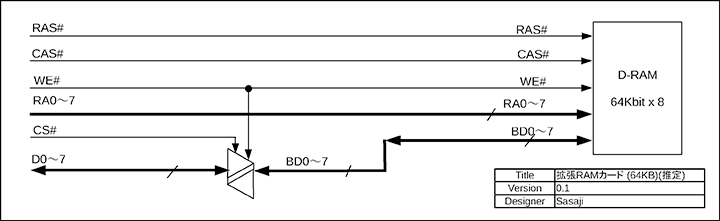

拡張RAMカードのブロック図を以下に示しました。各信号は本体側で生成されるので拡張カード側はかなり単純です。どうやら64KbitDRAM専用に設計されているようです。端子から出ている電源も+5Vだけだし(ちなみに16KbitDRAMは+5Vのほか+12Vと-5Vが必要)。

ではFPGA内部の実装を考えていきます。今回もMAX10-FB基板にあるSDRAMを使用します。機能としては…

- SDRAMへのアクセスは付属しているSDRAMコントローラを使用する。ただし、SDRAMリフレッシュとL3からのアクセスタイミングが重ならないように修正を加える。

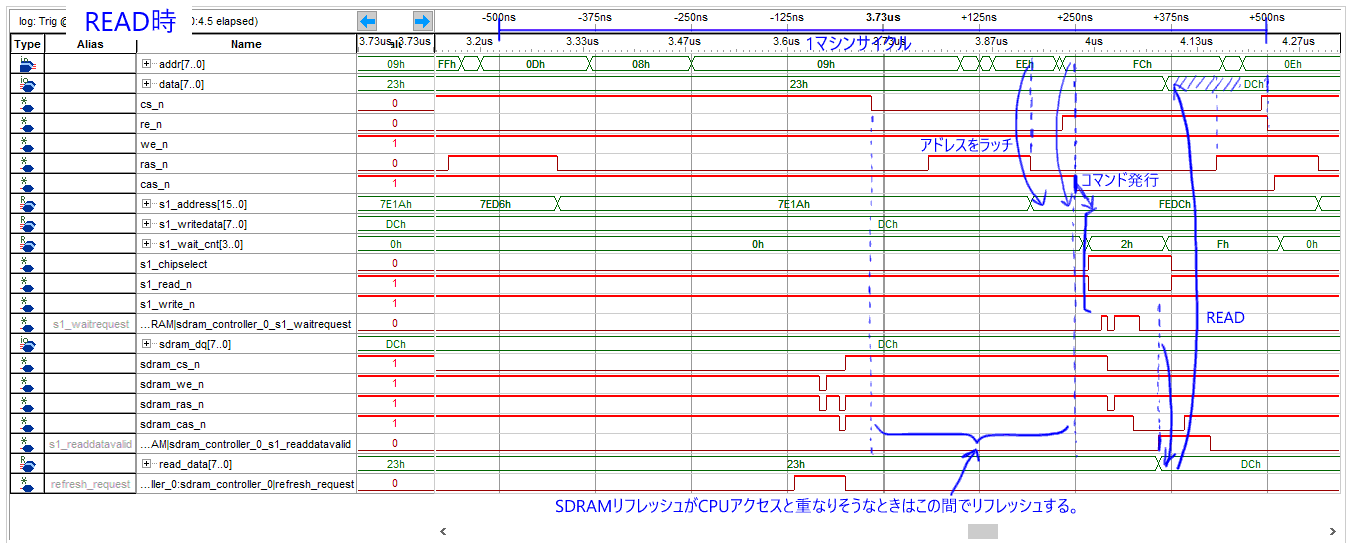

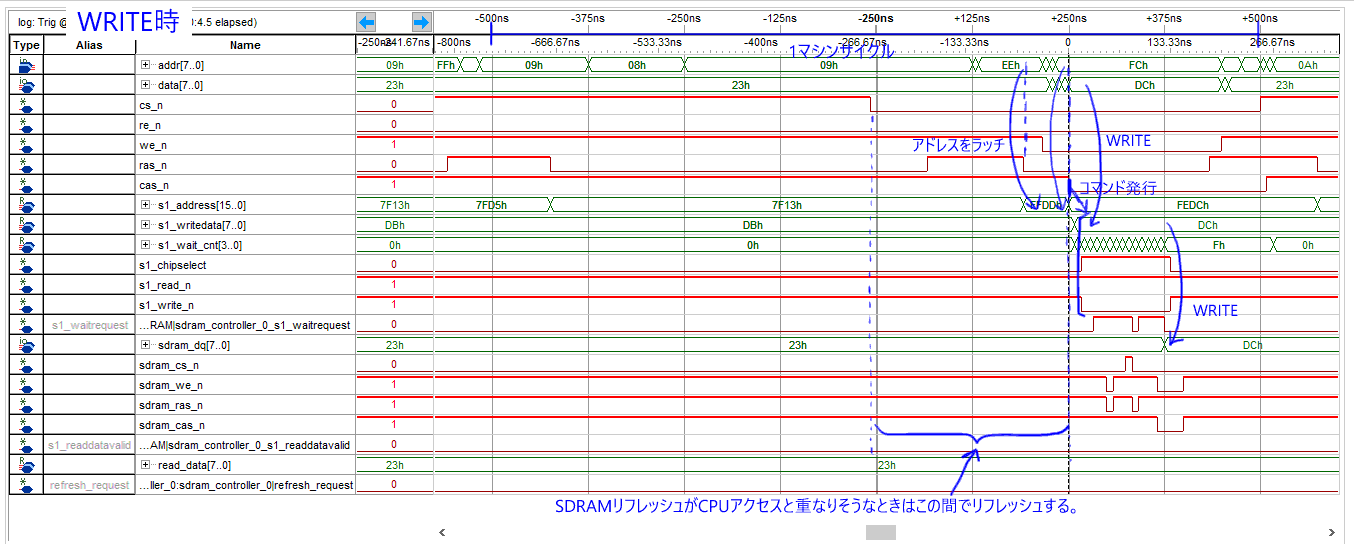

- L3からのRAS,CAS信号の立下りで行と列それぞれのアドレスをラッチし、CAS信号の立下りでSDRAMにコマンドを送る。

- SDRAMにコマンド送ってからRAS信号が立上がる(約125ns)までにデータを返すためSDRAMは120MHzで動かす。

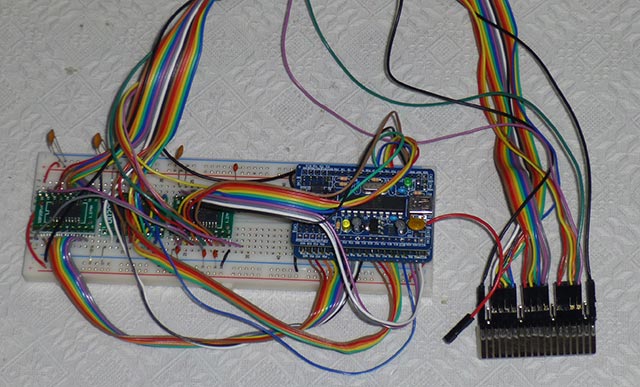

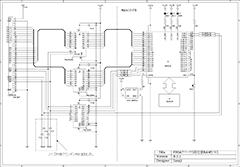

次に、FPGA周りの回路を設計します。前回と同じような回路ですがアドレスバスが8本と少なくなりました(回路図は後掲)。

接続が完了したらマーク5の電源を入れてみます。見た目では分からないのでメモリチェックプログラムをLOAD & RUNします。 結果は予想通りNG。毎度おなじみのロジアナで波形観測。まず見えてきたのは… SDRAMリフレッシュとマーク5のアクセスタイミングと重なることがあること。これはCS信号が立下がってからデータアクセスするまでに若干の余裕があるので、ここでリフレッシュするように変更しました。

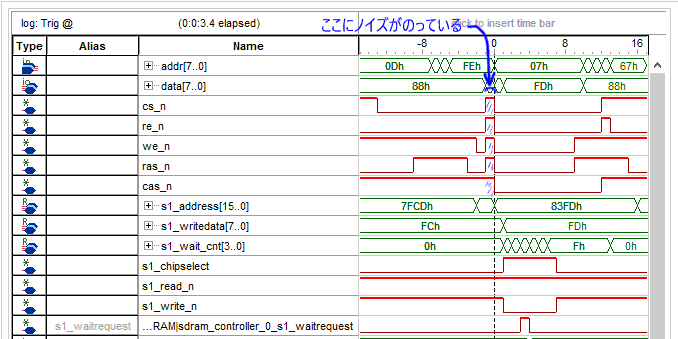

修正したら再度メモリチェック。お、前半の32KBはOKとなりましたが後半32KBはNG。さらに波形を詳細に観測していると…

どうもFPGA内部の回路で使用しているステートマシンが不正な状態になるようです。ソースコード上では状態0,1,2,3の4パターンしかないはずなのに、それ以外の状態になるなんて聞いてないよ…。なので、ステートマシンを使わないように変更しました。

再々度メモリチェック。うーん、まだ改善しない。しばらく波形を観測していると、どうやらWE信号がLになったあとにノイズ?が発生しているようで一瞬CS,RAS,CAS信号がHになってしまうことある、ことが分かりました。このノイズをとり除くためHDLで記述しようとしましたがうまくいかない。そこで回路を修正することに。CS,WE,RAS,CASの各信号線にコンデンサを接続することにしました。

さあ、これでどうだ!?結果は…おお、見事にOKとなりました。なお、コンデンサの容量を100pFにすると信号が遅延しすぎるようでメモリチェックがNGとなりました。

(訂正:回路図にあるコネクタ ピン26がOEと負論理になっていますが、正しくは正論理です。)

ちなみに、タイミングチャートは以下のようになります。

まとめ

今回は、FPGAのステートマシンの動きにハマってしまったこと、そして信号線にノイズがのること、これらの解決に苦労しました。このノイズがFPGAを接続していることに起因しているのか、はたまた本体固有の問題なのかは不明ですが、電子回路にはノイズ対策が欠かせないことを改めて感じることができました。(おわり)

ソースコード・ダウンロード

l3mk5exmem_010_source.zip (181KB)

[MD5:4921346d30815e4a1ef180924af325b6]

※試される方は自己責任でお願いします。

◆関連ページ◆