S1のバスを乗っ取る

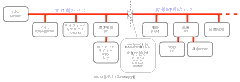

前回はFPGAからレベル3内のメモリへ直接アクセスできること、また、MB-S1のB(L3)モードでもアクセスできることを確認しました。今回は、MB-S1のA(S1)モードで本体内のメモリへ直接アクセスできることを検証していきたいと思います。

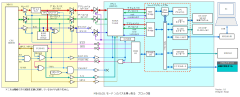

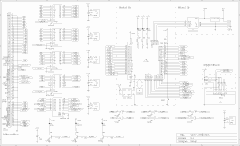

MB-S1のA(S1)モード用に変更

S1モード用に合わせてFPGA内部の構成を少し変更します。バスについての詳細は前回の記事を参照ください。

主な変更点を説明すると、

HALT信号のテスト

まずはHALT信号をONにし、グラフィックVRAMに直接アクセスして画面を表示させてみます。

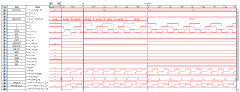

HALTの場合、MPUE信号が動作しているので、これを基準にしてバスにアクセスすればいいですね。WAITが必要な時も本体内のアドレスデコーダで判断してくれるのでFPGA側で余分な処理も不要です。

グラフィックは問題なく表示されました。

DMA信号のテスト

つぎはDMA信号をONにし、グラフィックVRAMに直接アクセスしてみます。

DMAの場合、MPUE信号が停止してしまうため、これを基準にアクセスできなくなります。このためFPGA側からのアクセスはE信号を基準にした1MHz駆動となります。

また、MPUE信号が停止したままになるとCPUの動作が不安定になる問題があります(前回の記事を参照)。 そこで、今回はDMA信号を2マイクロ秒ごとにON/OFFを切り替えるようにします。2MHz駆動時は4サイクル、1MHz駆動時は2サイクル毎に切り替えることになります。

では、DMA信号をONにします。ONにした途端にカーソルが改行を始め、そのうち画面が白くなる事態に…。この時点でメモリへのアクセスは行っていません。

試しにWAIT信号をONにしCPUを1MHz動作に落とした後、再びDMA信号をONにしてみたところ、先ほどの現象は出なくなりました。どうやら2MHz動作で何らかの問題があるようですがよくわかりません。ここで、グラフィックVRAMに直接アクセスしてみましたが画面に変化はなし。

そこで、一度グラフィック画面を表示させてから再度アクセスしてみました。

絵はスクロールしますが色情報が反映されません。どうやらMPUE信号が止まったためグラフィックI/O($FFE2x)が機能していないと思われます。スクロールは動作しているのでメモリコピーは問題ないようです。

マルチバスコントロール

最後はマルチバスコントロールについて少しだけ。

MB-S1はマルチバスコントロール(MBC)という本体側と拡張I/F側のバスを切り離す機能を実装しています。これを使えば拡張I/F側に別のCPUを繋げて本体側と独立して動かすことができます。この機能を使用したものとしてZ80Bカードや68008カードなどがあります。

BASICプログラムは拡張I/F側にある増設メモリに置かれています。通常、LISTコマンドを実行すればプログラムが表示されますが、MBC信号をONにすると表示されなくなります。

実際にCPUを独立して動かすには、BREQ OUT, BG IN信号や、増設RAMを本体側の制御から切り離す信号を駆使する必要がありますが、ここでの説明は割愛します。

以上の様子を動画にまとめましたので興味のある方はどうぞ。

まとめ

DMAはメモリアクセスが1MHz駆動であったり、グラフィックI/Oが機能しないなど制限が多いことが分かりました。ダイレクトメモリアクセスという名の通りあくまでメモリのコピーに特化しているようです。レベル3の拡張カードのために残している機能のようにも思えます。 MB-S1ではHALT信号を積極的に使用したほうがいいのではと感じました。

マルチバスコントロールについてはもう少し詳しく検証したいところですが…いつになることやら。(おわり)

参考文献

- I/O別冊ベーシックマスター活用研究 - 工学社

- I/O別冊S1活用研究 - 工学社

- HD6809E MPU Datasheet - HITACHI

◆関連ページ◆