レベル3のバス乗っ取り大作戦

いきなり昭和のマイコン雑誌のようなタイトルで恐縮ですが、今回はFPGAからレベル3のアドレスバスとデータバスを操作してレベル3内のメモリの読み書きを、同時に各信号の遷移を観測して内部の動作を確認していきたいと思います。

バスを乗っ取るって何?

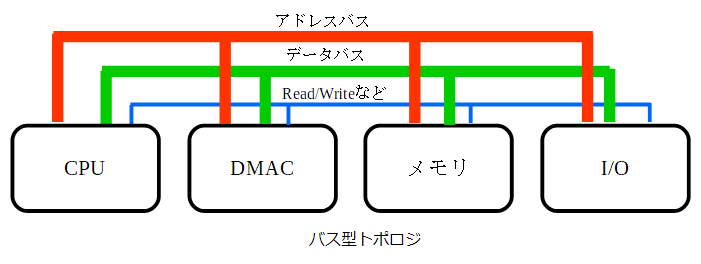

この頃のパソコンは一般的にバス型トポロジで1本のアドレスバスと1本のデータバスにCPUやメモリがぶらさがっているような形態です。通常バスを占有しているのはCPUで、同時に複数の機器がバスを使用することはできません。他の機器がバスにアクセスするためには、まずCPUを一時的に止めてバスを解放してもらう必要があります。

CPUのようなバスを占有する機器をバスマスタと言います。CPU以外によく使われるバスマスタと言えばDMAC(ダイレクトメモリアクセスコントローラ)があります。メモリコピーを高速で行いたい場合がありますが、この場合はCPUからDMACにバスの占有権を渡してDMACがメモリの読み書きを行い、終了すればまたCPUに占有権を戻すようなことを行います。

まあ、バスを乗っ取る、と言うよりバスを共有する、といったほうが正しいかもしれません。

CPUを一時的に止めるには

レベル3はCPUに6809を採用しています。このCPUには自身を停止させる信号としてDMA信号とHALT信号を持っています。

DMA信号をONにすると6809は次のサイクルで直ちに停止します。ただし停止後15サイクル(デッドサイクルを含む)毎にバスを要求してきます。2サイクルだけバスを占有した後また停止して15サイクルでまたバス要求、を繰り返します。6809としてはデッドサイクルを含めた16サイクル毎に1サイクルだけ動作する感じになります。

HALT信号をONにすると6809は現在実行中のコマンドが終了した時点で停止します。HALT中、RESETやNMI割り込みはHALTが解除されるまで保留に、他の割り込みは無効になります。

6809が停止状態になると6809から出ているBA信号およびBS信号がONになりますので、これを契機にしてバスへのアクセスを行えばいいことになります。

これらのタイミングチャートがHD6809のデータシートに載っています。これと実際に観測した結果が一致するかどうかを検証します。

設計

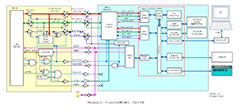

とりあえずブロック図を起こしたのでこれをもとにいくつか説明します。

ブロック図をもとに周辺回路も設計します。

レベル3とFPGAの間は毎度恒例のバッファを介して接続します。今回はバスやR/W信号を双方向バッファ74LCX245で接続します。DMAやHALTなどレベル3に渡す信号はオープンコレクタ74LS06を、FPGAに入力する信号は74LCX244で接続します。 DMA, HALTの各信号はONになっていることが分かるようにLEDを接続します。 BA,BS,VMA OUTの各信号は観測用で制御には使用しません。

実装

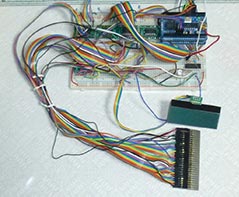

今回は、使用するICが多いためブレッドボード(大)を2枚つなげて実装しました。

これをレベル3の拡張I/Fに接続して準備完了。

レベル3マーク5実機でテスト

それでは電源ON。FPGAからDMA信号をONにします。オレンジ色のLEDが点灯したのでここでレベル3のキーボードを押してみると、通常より低いクリック音とともにキー入力ができます。CPUは先ほど説明したように16サイクル毎に1サイクルだけ動きます。言い換えれば通常の1/16のスピードで動作していることになります。

以下はFPGA内のロジアナで観測した信号の挙動です。

次に、HALT信号をONにします。紫色のLEDが点灯したのでレベル3のキーボードを押してみましたが反応がありません。CPUが完全に停止しているようです。

いずれも、HD6809のデータシートに載っているタイミングチャートと同じ結果が出ていることが確認できました。

信号観測だけでは実際に動いているのかいまいちわからないので、レベル3のVRAMに直接書き込んでみることにします。NIOS IIマイコンを使用してVRAMをリード・ライトして1ライン下にスクロールさせ、1ライン分の画像データをSDRAMからVRAMに転送する、を繰り返すプログラムを実行させてみました。

お、スクロールが始まり画像が出てきました。スクロールスピードはレベル3のソフトウェアで動かした時と比べると明らかに速いですね。 下のHALT信号では正常でしたが、上のDMA信号では途中で色が変わったりしました。これは、おそらくCPUがカラーレジスタを更新するためだと思われます。

以下はリード・ライト時のタイミングです。

アドレスバス、データバスにセットアップするタイミングはE信号の立ち下がりからQ信号の立ち上がりまでのほぼ中間ぐらい(約125ns)にしています。リード時、データはE信号の立ち下がりで取り込みます。

MB-S1でも・・・でもその前に

さて、レベル3でうまく動いてくれたようなので、今度はMB-S1のL3モード(Bモード)でも動くかどうか検証していきたいと思います。と、その前にレベル3と違う箇所について説明します。

MB-S1はCPUに68B09Eを採用しています。このCPU、HALT信号は持っていますがDMA信号は持っていません。なのでMB-S1はレベル3と互換を保つため独自でDMA信号を処理するように実装されています。

DMA信号をONにするとカスタムICであるYGM-001が、CPUに供給しているクロックMPUE信号とMPUQ信号を止めることで実質CPUが停止。その後にHALT ACK信号を送るようです。この辺のタイミングチャートが資料にないので実機テストで確認します。

VMA OUT信号はCPU由来のAVMA信号から生成しています。図にはありませんが、VMA CTRL信号は本体内部のアドレスデコーダの有効無効も制御しているので本体内部にアクセスする場合はONにします。

HALT信号はレベル3と同じようにCPUが受け取ります。

MB-S1実機でテスト

それではMB-S1の拡張I/Fに接続してテストといきましょう。

電源ONしてFPGAからDMA信号をONにします。LEDが点灯したのでキー入力するも反応がありません。どうやらレベル3とは異なりCPUは停止したままになるようです。

ここでDMA信号をOFFにするとMB-S1が勝手に再起動してしまいました。DMA信号のON/OFFを何回か試しましたがいずれも再起動かフリーズします。 68B09EのデータシートによるとクロックE,Q各信号の"H"や"L"の持続時間は最大9.5usとなっています。DMA信号を長時間ONにしてMPUE信号を止めてしまうとCPUが不安定になって再起動しまうのかもしれません。

ということで、DMA信号はONにした後、7サイクル毎に1サイクルだけOFFにする機能を実装しました。

一方HALT信号ですが、これはレベル3と同じ動作ですね。

では、画像データを表示させてみます。

上のDMA信号では色が反映されていません。レベル3と同じくCPUがカラーレジスタを更新するためだと思いますがよくわかりません。HALT信号のほうはうまく表示されました。

レベル3とMB-S1で動かした様子を動画にまとめましたので興味のある方はどうぞ。

【動画】レベル3のバス乗っ取り大作戦 動作検証 (YouTube)

まとめ

今回は、大げさなタイトルとは裏腹に思惑通りに動いてくれましたので苦労する箇所はほぼありませんでした。まあ、FPGAを使っているのでタイミング調整しやすいことが大きいかと思います。

DMA信号の扱いがレベル3とMB-S1ではかなり異なっていますが、これを使用するボードの互換性はどうだったんでしょうか。6800ファミリーのDMACであるMC6844のデータシートにはCPUとDMACを数サイクル毎に交互に動かすような回路が載っていましたのでDMA信号はON/OFFを繰り返すのが前提なのでしょうか。うーむ謎ですねぇ。

てなわけで次回は、MB-S1のS1モード(Aモード)で1Mバイトのアドレス空間にアクセスできるか検証してみたいと思います。(つづく?)

参考文献

- I/O別冊ベーシックマスター活用研究 - 工学社

- I/O別冊S1活用研究 - 工学社

- HD6809 MPU Datasheet - HITACHI

- HD6809E MPU Datasheet - HITACHI

- MC6844 DMAC Technical Data - Motorola

◆関連ページ◆