◆マーク5専用拡張メモリカードの情報はこのページの下部にあります。

マーク5用の拡張メモリを作る その2

今回は、SRAMを用いてマーク5用の拡張メモリを作りたいと思います。 拡張メモリの概要は以前の記事に記していますのでこちらも参照ください。

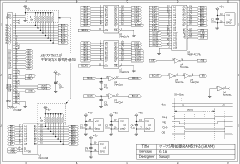

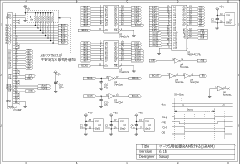

さっそく回路図から

いきなり回路図が2つありますが両者の違いは、回路図aにはデータバスに双方向バッファ(74HC245)を接続している、回路図bには接続していない、と1箇所だけの違いになります。内容について簡単に説明すると:

動作テスト

それでは、回路図aを実装して動作テストしてみます。 メモリチェックを行うと、ロジックアナライザを接続する前はOKでしたが、アドレスバスRA0~7にプローブを接続すると時々NGになります。アドレスバスにプルアップ抵抗10Kオームを付けたところOKになりました。

データバスBD0~BD7に付けているプルアップ抵抗はCMOS ICを使っているから、ですが、こちらははずしても動作しました。

次は、回路図bを実装してメモリチェックをしてみます。すると、こちらも回路図aと同じ現象になりました。ただ同じ対処でOKとなるので、データバスの双方向バッファの有無は動作に影響しないことが分かりました。

ロジックアナライザで観測した信号の様子は以下のようになります。

まとめ

ロジックアナライザをアドレスバスに接続するとメモリアクセスが安定しなくなる現象がありましたが原因はよくわかりません。TTLとCMOSの違いからくるのか、はたまた本体側のバッファが経年劣化でドライブ能力が下がっているのか、いろいろ考えられそうですが…。

今回は、SRAM1個とロジックIC3個で実現できるのでかなりお手軽です。が、私はこの拡張メモリを使用するソフトに出会ったことないんですよねぇ。本当に必要なの!?と根本的な話になってしまいそうなのでこのへんで終わりにします。

参考文献

- I/O別冊ベーシックマスター活用研究 - 工学社

マーク5専用拡張メモリカードを作成しました

ダウンロード

Rev.0.1

- 基板設計 CADデータ (Board Design CAD Data) (Autodesk Eagle 9.6) - l3mk5exmem_010.zip (529KB)

[MD5:66a1c9057351d1766a6b6741d2f1dfff] - 説明書・部品表 (.pdfファイル)

- 上記ファイルはGitHub(https://github.com/bml3mk5/L3mk5ExRam)にもあります。

◆関連ページ◆