FPGAでFDDコントローラを作る (5) ライト処理

前回でディスク吸い出し装置としては一通り完成しました。今回は、さらにディスクイメージを書き込む機能を実装してみたいと思います。

書き込みに必要な信号

書き込み用の信号はWRITE GATEとWRITE DATAの2つです。WRITE GATE信号をONにしている間ディスクに書き込みが行われます。WRITE DATAにはデータパルスを入れます。データパルスについては過去の記事を参照ください。

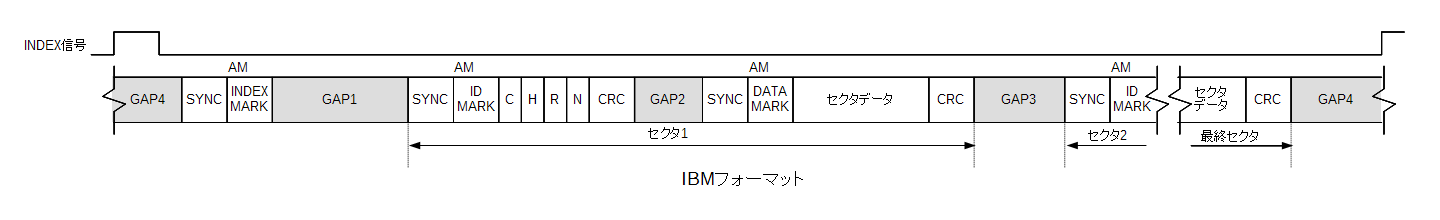

ディスクのフォーマットなど1トラックを書き換えるような時はINDEX信号を基準にして書き込めばいいですが、セクタ単位で書き換える時はトラック番号やセクタ番号を読み込み一致したセクタでセクタデータを書き込むようなリードとライトを協調させる処理が必要になります。今回は簡単な1トラックを書き換える処理だけを実装します。

書き込み処理を考える

ディスクイメージはD88形式からIBMフォーマットに即した形式にするためGAP,SYNCフィールドなどを追加します。PC上でこの処理を行った後、FPGA側のSDRAMに送るようにします。ここはPC,FPGA双方ともソフトウェアで行います。

FPGA側ハードウェアではINDEX信号を検知したらWRITE GATE信号をONにして、以下のように処理していきます。

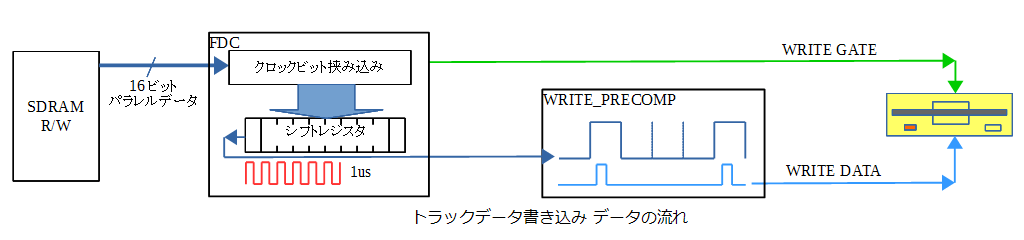

- SDRAMから2バイトデータを読みこみ。

- 読み込んだデータからミッシングクロックかどうかを判定。

- データの各ビットの間にクロックビットを入れる。

- これをシフトレジスタへ。2HDの場合は1マイクロ秒ごとにシフトさせる。

- 上記ビットが1の時に、一定期間パルスをWRITE DATA信号として出力。

2.や3.はPC側のソフトウェアで行えばFPGA側ハードウェアで処理する必要がなくなりますが、今回はあえてFPGA側ハードウェアで頑張ってみます。では、各処理を簡単に説明していきます。

SDRAMから読み込む

SDRAMからは、INDEX信号を検知する前に2バイトに先読みしてFIFOバッファに入れておきます。バッファが空になったら次の2バイトを読み込む、を繰り返します。

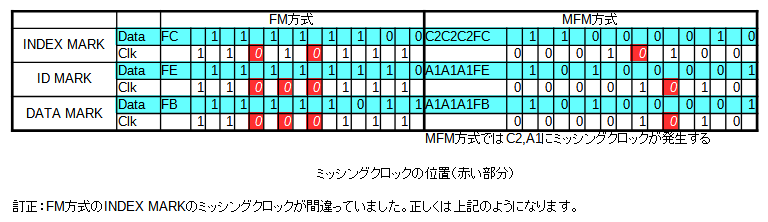

ミッシングクロックの判定

FIFOバッファのデータをIBMフォーマットに照らし合わせて、そのデータがAMフィールド(INDEX MARK, ID MARK, DATA MARKの部分)であれば一部のクロックパルスを発生させないようにフラグを立てます。

クロックビットを挟み込む

データビットの間にクロックビットを入れて32ビットの新たなデータを作成します。クロックビットの入れ方はFMまたはMFM方式に従います。上記でフラグが立っているビットはミッシングクロックとなるためクロックビットを0にします。

WRITE DATA信号の出力

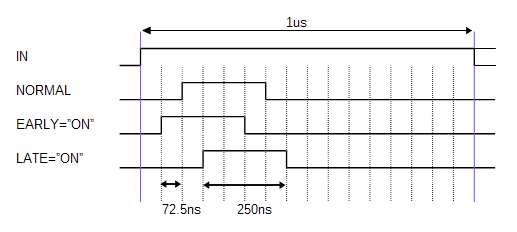

上記データは32ビットのシフトレジスタに入れます。2HDの場合は1マイクロ秒ごとに左シフトさせてシリアルデータにします。このデータが1の時は、250ナノ秒幅のパルスをWRITE DATA信号に出力します。

改めて内部構成と周辺回路を確認

内部構成については、上記機能をFDCモジュールに実装していきます。周辺回路については、回路は同じですがロジックICに74LS06を使用することにしました。データシートを見る限りこちらのほうが信号遅延が少ないようなので。

波形を確認

シミュレーションと実機での試行錯誤の結果、想定通りに動かすことができましたので、実際に書き込まれたかを確認してみます。

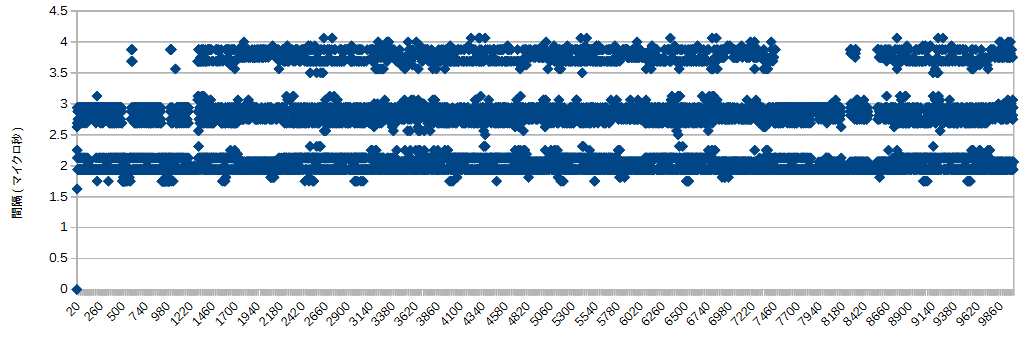

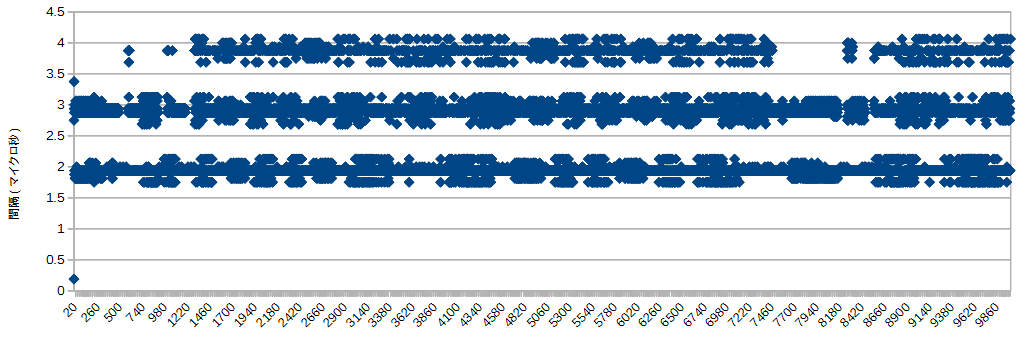

書き込まれているのは確認できましたが、かなりばらつきがあるようです。さらに細かく見ていきます。

例えば3マイクロ秒から2マイクロ秒に変化する部分では本来2マイクロ秒である部分が長くなり、一方で3マイクロ秒である部分が短くなっています。パルス間隔が2.5や3.5マイクロ秒になるとリード時の判定で誤認識する可能性もあります。そこで補正をかけてこのばらつきを抑える必要があります。

書き込み補償(Write Precompensation)とは?

パルス間隔が変化する部分では、干渉などによりどうしても理想のパルス位置よりもずれてしまいます。そこで書き込み時にあらかじめずれることを想定して補正を行います。

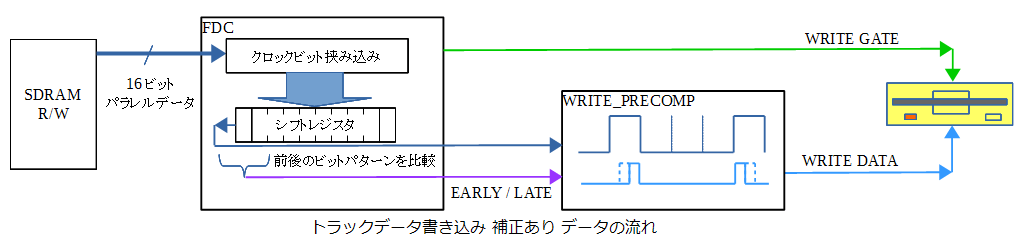

実装としては、シフトレジスタから1ビットづつデータを出力する際に前後のビットパターンを調べて、補正をかけるか否かを判断するようにします。補正が必要ならEARLYまたはLATE信号をONにして、後段のWRITE_PRECOMPモジュールでこれらの信号に合わせてパルスの出力をすこしずらします。

今回は、どれくらい補正していいかわからなかったので、何パターンかを試してみました。その結果、補正対象にするのは:

- 2→3または4マイクロ秒に変化する時、72.5ナノ秒(16MHz相当)早くする。

- 3または4→2マイクロ秒に変化する時、72.5ナノ秒(16MHz相当)遅くする。

このパターンで、かなり補正できることが分かりました。

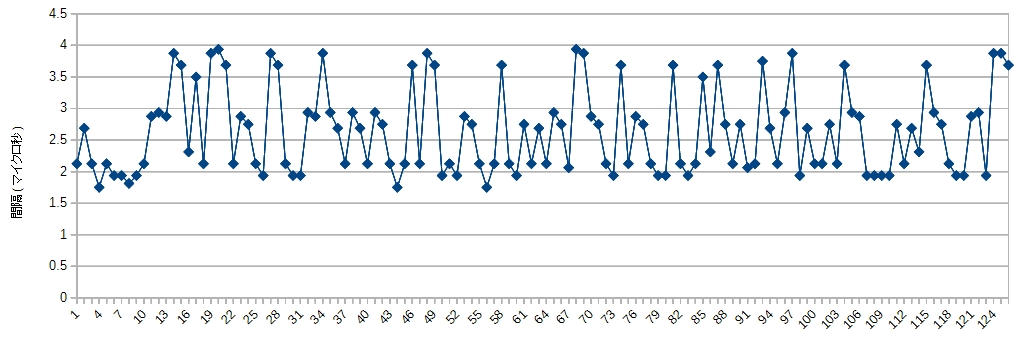

再度波形を確認

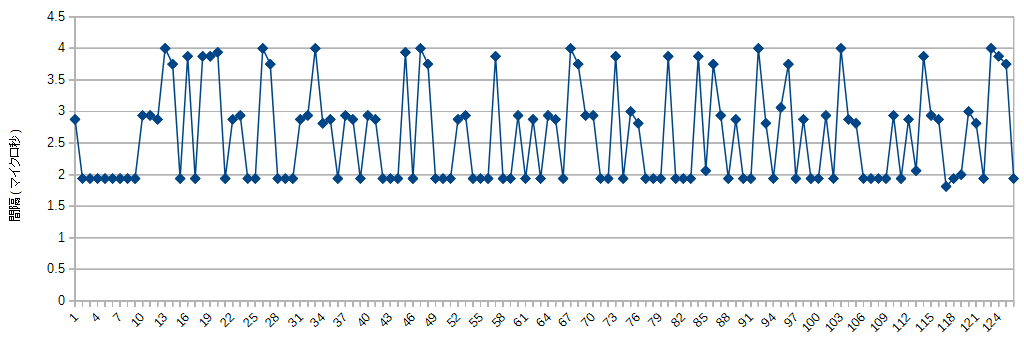

補正ありで書き込みを行った結果を確認してみます。

補正前よりはまとまった感じになりました。

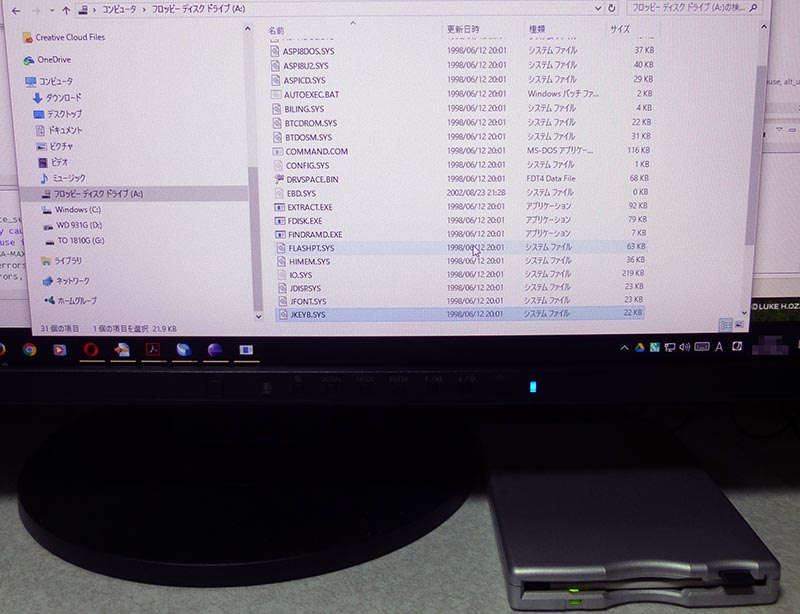

つぎに、ディスク全体をWindows98の起動ディスクのイメージに書き換えてPC上からディスクが見えるかを試してみます。

PCにUSBフロッピーを接続し、書き換えたディスクを入れてみます。お、ファイル一覧が表示されました。テキストファイルも見えましたのでうまく書き込めたようです。

5インチ 2HD FDDでも確認

S1の5インチ 2HD FDDでも試してみます。これの補正ですが、S1のサービス技術資料などを見ると、トラック番号が43より大きい場合に125ナノ秒のずれで補正するようです。5インチだと外周は記録密度が低く干渉が少なくなるので補正は必要ないということでしょうか。

ということで、補正対象にするのは:

- 2→3または4マイクロ秒に変化する時、125ナノ秒(8MHz相当)早くする。

- 3または4→2マイクロ秒に変化する時、125ナノ秒(8MHz相当)遅くする。

- これらは、トラック番号が43より大きい場合のみ行う。

また、パルス幅も125ナノ秒にします。

内容を確認した結果、問題なさそうなので、ディスク全体を書き換えてS1で読み込みできるかを試してみます。以下の動画は、S1用OS-9のディスクをDISK BASICに書き換えて起動するまでを録画したものです。興味ある方はどうぞ。

【動画】5インチ2HD フロッピーディスク書き換え 動作検証 (YouTube)

これで、ディスク書き換え装置としても使えるようになりました。もうこれで怖いもんなしです(?)。FDの知識も(今更ながら)つきましたので、これを何かに活用したいところですが、L3/S1用仮想FDDの改造でもやってみようかなぁ。(おわり)

参考文献

- FDアダプタ - http://ldlabo.hishaku.com/NO46/main.htm

- MB-S1 30/40 サービス技術資料, 日立

- マイクロコンピュータMC6809の考え方, オーム社

- FUJITSU MB8877A Datasheet