FPGAでFDDコントローラを作る (3) データセパレータ

前回ではFDDから生データを読み出してPCにダウンロードする所まで実装しました。今回は、生データをデータセパレータに通して1トラック分のバイト列として取り出せるように実装していきたいと思います。

データセパレータとは?

FDDの生データにはデータパルスとクロックパルスが含まれています。ここからクロックとデータ成分に分離するのがデータセパレータです。これを実現する回路としてよく用いられるのがVFO回路です。このことから、一部のサイトや文献ではデータセパレータを単に「VFO」として説明しているところもあります。

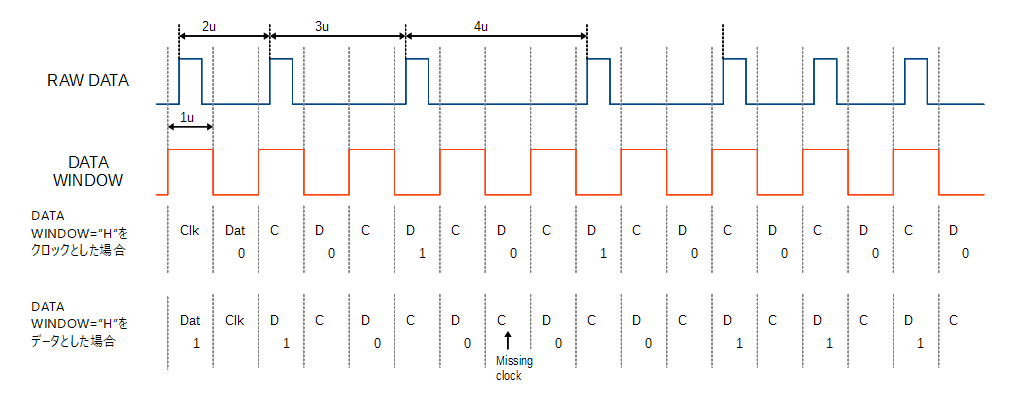

処理としては、生データのパルスと同期するようにデータウィンドウとよばれるクロック(図の赤い線)を生成してFDCに渡します。FDCはこれを基準にしてデータを取り出します。

図は2HDの場合を示しています。データウィンドウの周期は約0.5MHzですが、生データのパルスに合わせて周期を調整します。データ成分はデータウィンドウが"H"のときか"L"のときかで2パターン出てきますが、これはフォーマットと照らし合わせて決定することになります。

データセパレータを実装

それでは、データセパレータの実装を考えていきます。

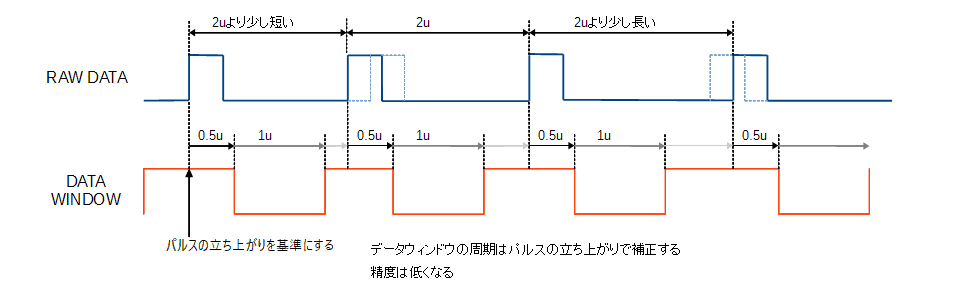

生データ(RAW DATA)パルスの立ち上がり(註:FDDから出る信号は負論理なので波形を上下逆転させてます。)を基準にして、0.5マイクロ秒後にDATA WINDOW信号を反転させて、1マイクロ秒後にまた反転させる、を繰り返します。

この周期は24MHzのカウンタ回路から生成します。パルスの立ち上がりでカウントをクリアし、その後は24MHz周期でカウントアップ、カウント値が12,36,60でDATA WINDOW信号を反転、という実装になります。ところで、なぜ24MHzにしているかは後で述べます。

この方法、RAW DATAパルスの間隔がばらついていると精度が悪くなりますが、前回調査したパルス間隔の分布が意外とまとまっていたので、さほど問題にはならないと判断しました。

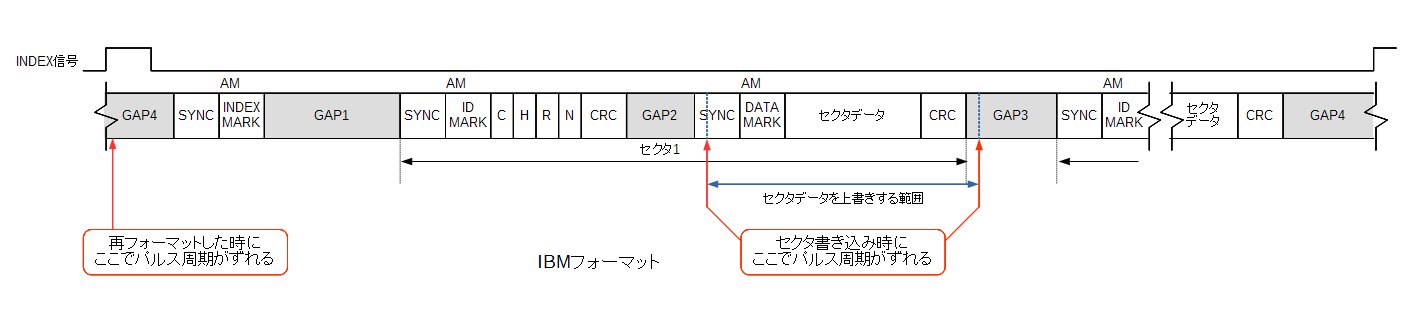

パルス周期がずれる

パソコンのOSがFDに書き込むデータ単位はセクタ毎なので、上書きが始まる境界と終わる境界ではどうしても元からあるデータとのパルス位置がずれてきます。今回の実装ではデータパルスの間隔が1.5~2.5~3.5~4.5マイクロ秒の範囲外なった場合は単純に無視することにします。

ただし、パルスがずれるとDATA WINDOW信号もずれる可能性があるため、GAP,SYNC,AMの各フィールドを検出してDATA WINDOWが"H"の時がデータ成分であるように常に調整するようにします。

データ成分を取り出す

生成したDATA WINDOW信号はFDCモジュールに入れて、ここでデータを抽出します。

抽出したデータはシフトレジスタに入れ最終的にSDRAMに書き込まれます。ここは、前回の生データの取り出しで実装した部分をそのまま使います。

ここまで実装したら例によってシミュレーションで確認です。今回は生データがあるのでこれをテストデータとして使用します。そうそう、ソフトウェアのほうも1トラック分のデータが取り出せるようにコマンドを追加します。

実機でテスト

では、実機でテストをします。案の定うまくいきません。この辺は毎回のことなのでもー詳しい過程は省略です。。。

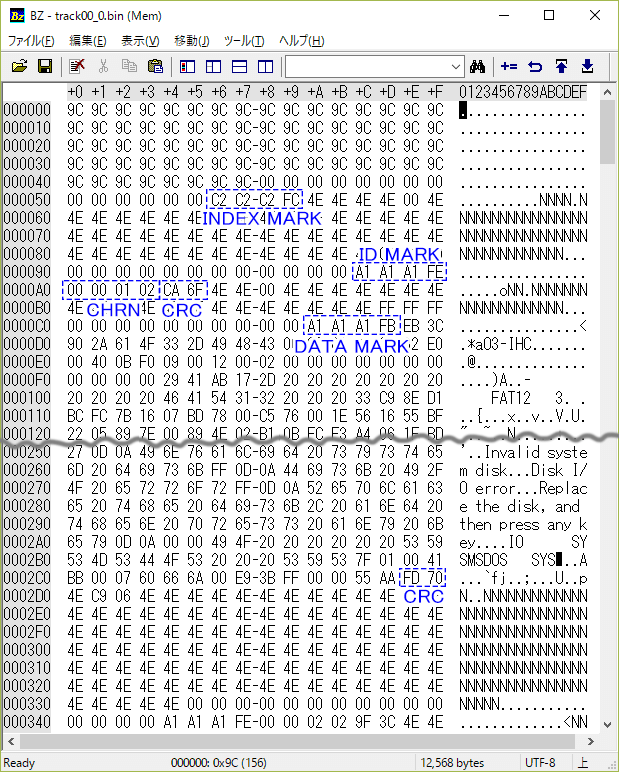

試行錯誤して、なんとか1トラック分のデータを取り出すことができました。1トラック分のデータサイズは1ビットが2マイクロ秒なので200000(us)/2(us)/8=12500バイトとなり、写真の数値とほぼ合っていることが分かります。これをPCにダウンロードして、取り出したデータをバイナリエディタで確認してみます。

これは、Windows98の起動ディスクですが、FAT12なんて文字列も見えますね。データ最初のGAP4の部分が9Cと違う値になっていますが、これは先ほど述べたパルス周期のずれによるものです。

さて、データが正しいかどうかはセクタの最後にあるCRCと一致するかを確かめる必要があります。今回は、FPGAにCRCを計算する機能を実装していないのでPC側で別途ツールを使って計算しました。計算結果が一致したので正しく取り出せたようです。

2DDのディスクでテスト

次は2DDのディスクを試してみます。2DDのデータパルスの波長は2HDの倍ですので、データセパレータの周波数は半分の12MHzにすればうまくいきます。取り出したトラックのデータサイズは半分の6250バイトとなります。

NEC PC-98のディスクでもテスト

NEC PC-98のディスクも読みだしてみます。使用しているFDDは3モードなので、MODE SELECT信号を切り替えれば読み出すことができますが、今回は、2モードFDDを想定して、FPGA側で調整して読み出すようにします。

前回でも少し述べたように、PC-98シリーズのFDDはモータの回転数が360rpmです。これを300rpmのFDDで読み出すとデータパルスの波長が長くなってしまいます。そこで、データセパレータの周波数を24(MHz)*300/360=20MHzにします。こうすることで長くなった波長に合わせられます。なぜ24MHzを使用していたかという理由はここにあります。

ここまでで、3.5インチの2HD,2DDそしてPC-98用2HDの各FDを読み出すことができました。あとは、全トラックを一気に取り出すようなバッチ処理をPC側のソフトに実装してやれば、ディスクイメージ吸い出し装置として使えますね。

さて、次回はドライブを変更して5インチFDDに対して、そして3インチコンパクトFDDにも接続してみてデータの取り出しを試してみたいと思います。(つづく)

参考文献

- FDアダプタ - http://ldlabo.hishaku.com/NO46/main.htm

- PC-9821/9801シリーズとFDD - http://www.geocities.jp/cpuparts98/FDD/FDD_0.htm

- マイクロコンピュータMC6809の考え方, オーム社

- TEAC FD-235HG-C304 MICRO FLOPPY DISK DRIVE SPECIFICATION

- FUJITSU MB8877A Datasheet

FDDコントローラを作る (2) ←前 | 次→ FDDコントローラを作る (4)