レベル3/S1用の仮想FDDを作る Part2

以前の記事でレベル3/S1用の仮想FDDを作りましたが、これはフロッピーディスクコントローラ(FDC)とフロッピーディスクドライブ(FDD)を一体化したものでした。今回は、FDDコントローラを作るで得たFDDの知識を生かして、FDD部分のみをエミュレートするものを作ってみたいと思います。このような製品としてはHxCフロッピーディスクエミュレータなるものがありますが、これに近いものを作ってみようというわけです。

レベル3 2Dの仮想FDDを作る

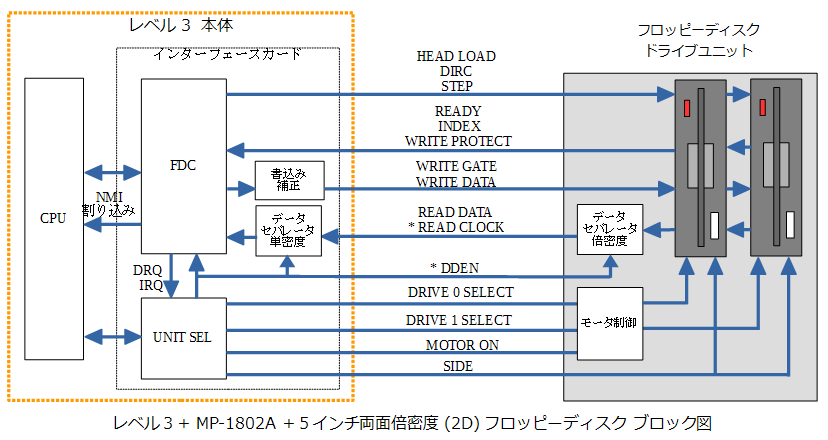

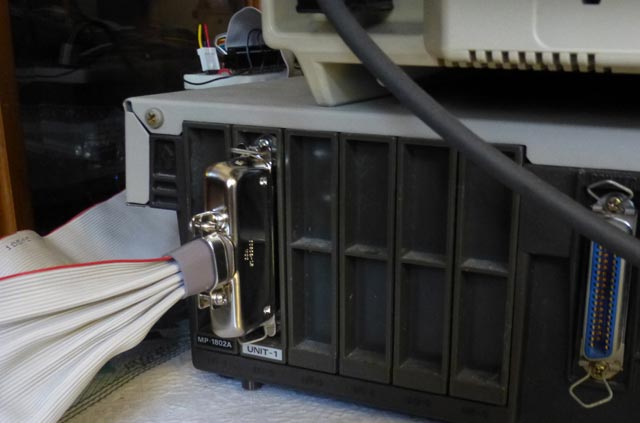

最初は、ベーシックマスターレベル3用の仮想FDDを作っていきます。レベル3側には拡張インターフェースにFDD I/FカードMP-1802Aを挿しています。これとFPGAを接続するための実装を考えていきます。

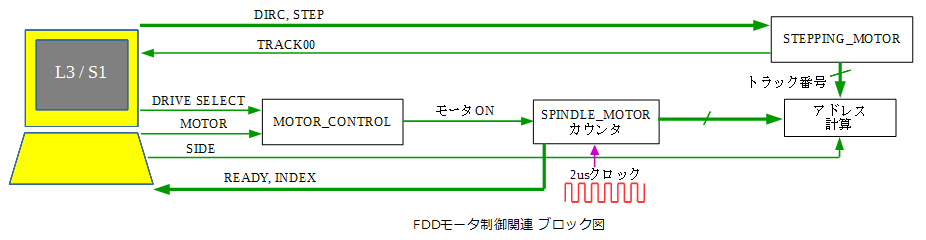

まずは、MP-1802Aと接続したときのブロック図を示しました。

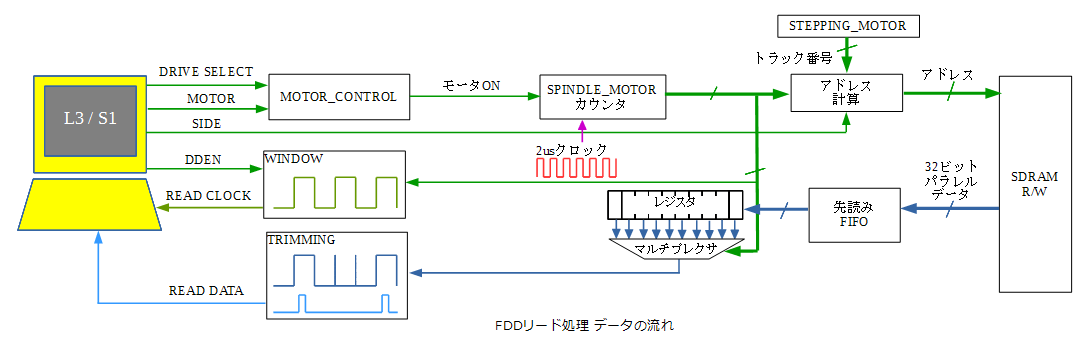

いくつか補足すると、DDEN信号は倍密度のとき"H"、単密度の時"L"となります。そしてREAD CLOCK。これはデータセパレータ(VFO)で生成したデータウィンドウ信号を入れます。倍密度、単密度で周期が変わるためDDENが必要になるわけですね。

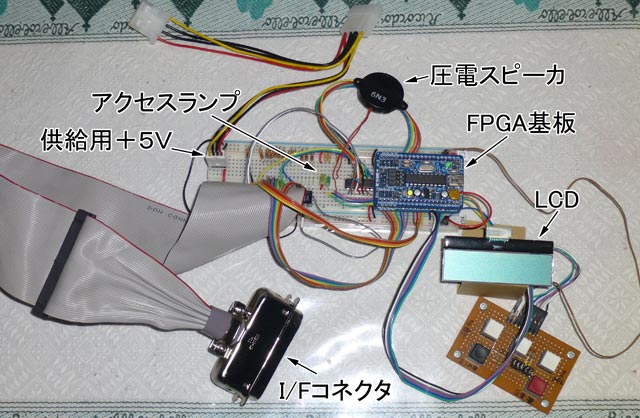

これをもとに回路を設計してみます。上記の信号のほかに、毎度おなじみの押しボタン、状態表示LCDを接続します。今回はさらにアクセスランプLEDと圧電スピーカ(ブサー)を追加します。圧電スピーカはヘッドを動かす操作をした際にビッっと音を出すようにしてFDDな感じを醸し出すようにします。

各信号はオープンコレクタなので入力側には10KΩのプルアップ抵抗を付けます。一方出力側はレベル3が+5VでプルアップされているのでロジックIC 74LS06を介して接続します。DRIVE 2 SELECT, DRIVE 3 SELECT, HEAD LOADの各信号は図にはありますが使用していません。

あと、MP-1802Aに外部から+5Vを供給する必要があります。これは別途、外付けHDDで使用していた電源を用いることにします。各ピンについてはこちらの技術資料も参照ください。

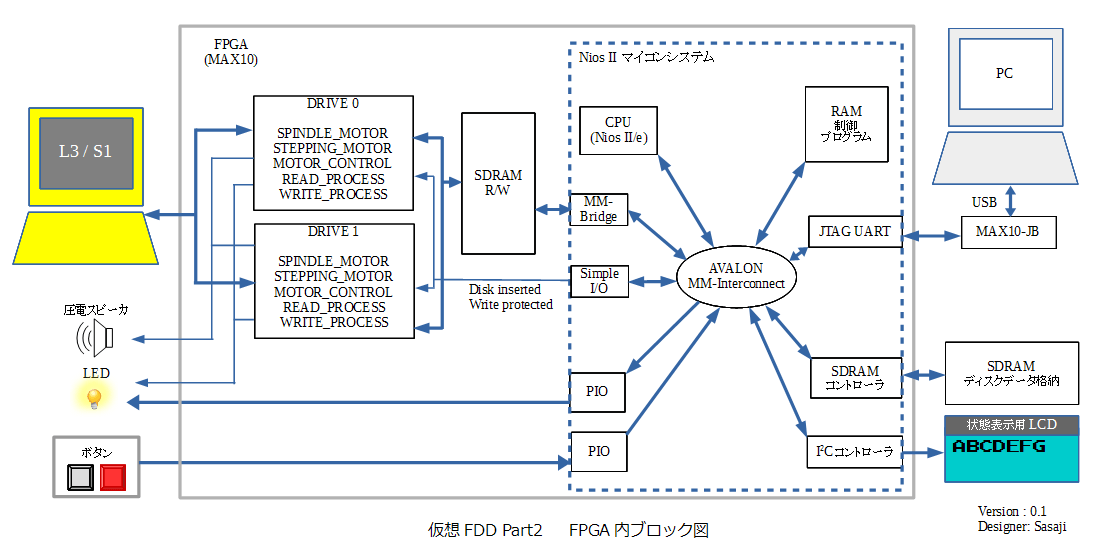

FPGAの内部を設計

ドライブ数は2ドライブ構成とします。ただし、さらに2ドライブ分のディスク退避用の領域を用意します。これはPCとのディスクイメージの送受信に若干時間がかかるため、ディスク入れ替えをすばやく行うための措置です。NIOSIIマイコンはPCとのデータ送受信のほか、ディスクが挿入されているかどうか、またライトプロテクトが掛かっているかの状態の変更もできるようにします。この辺りは以前作ったものを流用します。

ディスクは2Dなので2マイクロ秒ごとにクロック or データパルスをレベル3側に出力する必要があります。今回は処理を簡単にするためこのパルスを1ビットのデータとし、2マイクロ秒たてば次のビットを出力するというような構成にします。ディスク1周は200ミリ秒なので必要なデータ容量は1トラック当たり100,000ビット=12500バイトとなります。トラック数は40で両面(2サイド)なのでディスク1枚あたり12500*80=1Mバイトとなります。

DRIVE SELECT&MOTOR信号がともにONになればSPINDLE_MOTORモジュールにあるループカウンタのカウントアップを開始します。このカウンタは100Kで一周し0に戻ります。DIRCとSTEPパルス信号でSTEPPING_MOTORモジュールにあるトラック番号を増減させます。SDRAMのアドレスはループカウンタとトラック番号さらにSIDE信号から算出します。

カウントアップ中はSDRAMからデータをリードし、32ビットのレジスタに入れシリアルデータにしてREAD DATA信号として出力します。今回レジスタはシフトではなくマルチプレクサ(セレクタ)で各ビットを選択する実装にしました。

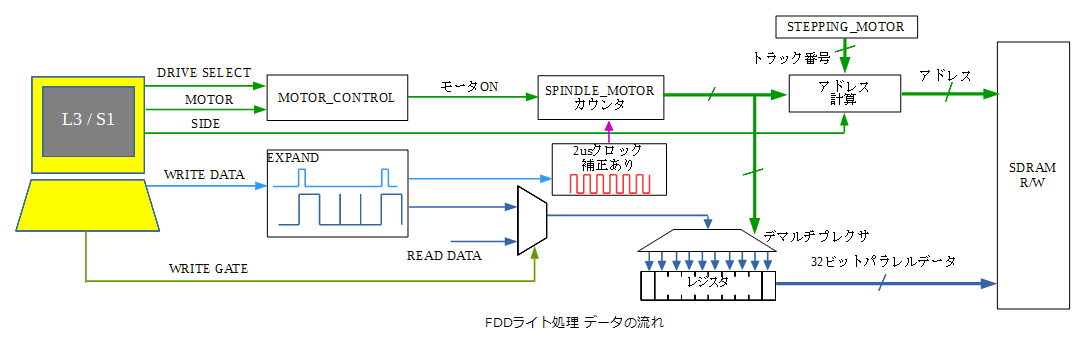

WRITE GATE信号がONになったときは書き込みを開始します。WRITE DATAにパルスが送られてくるのでこれを受けてパラレルデータにします。READ DATAのパルス周期とWRITE DATAのそれとは微妙に異なるので、書き込み位置がずれないようWRITE DATAのパルスに合わせてカウントアップ用の2マイクロ秒クロックに補正をかけます。これはデータセパレータと同じ考え方で実装します。

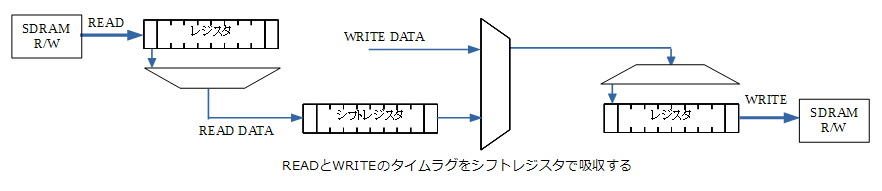

また、READ DATAとWRITE DATAにはFDC側でフォーマット解析を行うためタイムラグがあるはずです。具体的にどれくらいなのかがわからないので、ここは実機でのテストで調整することにします。

実装

それでは実装していきます。FPGA内部のモジュールは前回の仮想FDDやFDDコントローラで作ったものがあるのでそれらを流用します。実装したら想定通り動くかをシミュレーションします。ホスト側ソフトウェアはD88形式のディスクイメージをクロックビット&データビットを含んだFDの生データの形式に変換してFPGAに送るように実装します。回路は毎度恒例のブレッドボード上に実装し、コネクタをMP-1802Aに接続して準備完了。

実機でテスト

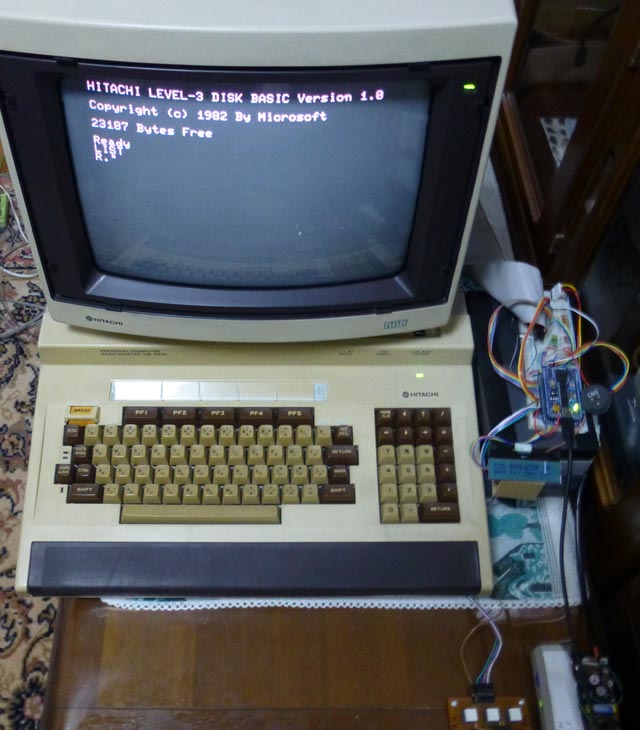

ではテストしていきます。LEVEL3 DISK BASICのディスクイメージをFPGAに送信したら、マーク5の電源を入れます。おっ、アクセスランプがついて圧電スピーカから音がしましたが……ROM BASICが起動しました…。

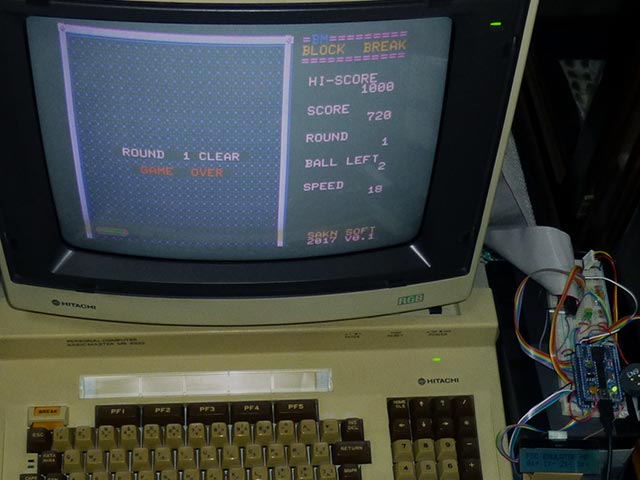

ロジックアナライザでREAD DATA信号を見るとデータが正しく出ていないようです。ハードウェア側を調べたがよくわからない。うーん、と思いディスクデータを見たところ、あれおかしい。結論としてホスト側のディスクイメージ変換処理にバグがありました。これを修正して再度トライ。おっ、DISK BASICが起動しました。ってオートスタートの設定になっているので拙作のゲームが起動してしまいました。

ライト処理

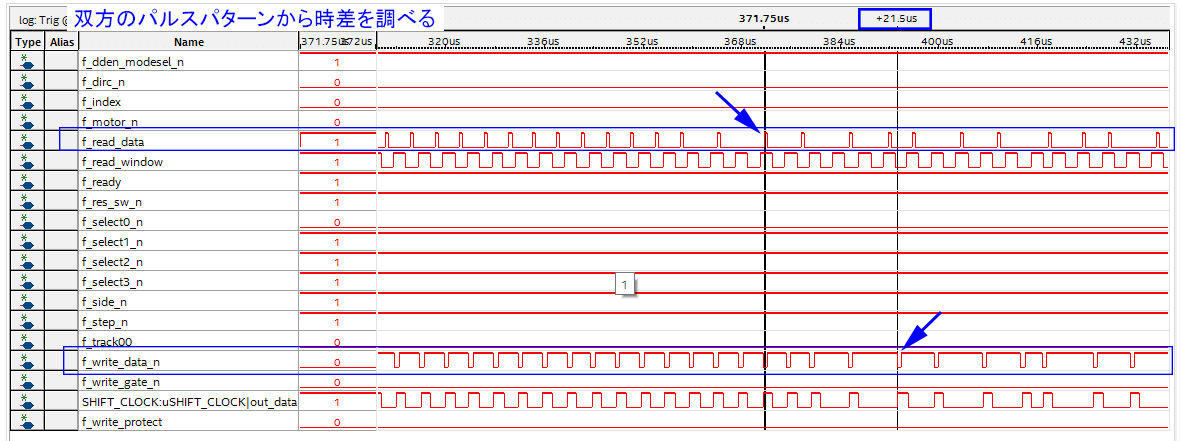

リード処理は問題なさそうなので次にライト処理のテストを行います。ここではまずREAD DATAとWRITE DATAのタイムラグを調べます。このタイムラグを考えないと書込み処理を行うたびにディスクイメージ内のセクタデータ位置がずれてしまい、最終的にデータが読めなくなってしまうことになります。最初は、DISK BASICからSAVEを行いこの時のREAD DATAとWRITE DATAのずれを観測しました。

双方のずれは約21.5マイクロ秒。これから書き込むデータビットのずれは11ビットとしました。このずれを吸収するためにREAD DATAを11ビットのシフトレジスタに入れてWRITE DATAとタイミングを合わせます。また、書き込み先のアドレスも11ビット分のずれを考慮して計算します。

上記の調整を行った後もう一度SAVEを行いました。書き込んだディスクイメージをPC側に送り検証したところ、書き込み開始が1ビットずれているところがありました。ただし、これは実際のFDでも起こりうることなので問題なしとしました。SAVEしたプログラムのLOADも正常に行えましたので大丈夫でしょう。

下の動画は、DISK BASICを起動してLOADとSAVEが行えるかを検証したものです。興味ある方はどうぞ。

【動画】日立ベーシックマスターレベル3編 動作検証 (YouTube)

MB-S1でも…

レベル3で問題なく動いたので、MP-1802AをS1に挿してこちらでも検証しようとしたのですが、拡張ボードのエッジコネクタ端子が微妙にずれるし奥まで入らない。レベル3用のカードを使うにはMPC-EX02SかMPC-EX04Sを使わないといけない、ということでここは素直にあきらめました。

というわけで、次回はMB-S1モデル40の2HD FDDを仮想FDDにして検証してみたいと思います。(つづく)

レベル3/S1用の仮想FDDを作る ←前 | 次→ レベル3/S1用の仮想FDDを作る Part3