マーク5用の9声PSGを作る

前回は6声PSGを実装しましたが、実は動作確認に使用したゲームは3声しか使っていないのでした。今回はPSGシリーズ第2弾ということで、月刊I/O 1983年8月号に掲載されたPSG(9声)カードの機能をFPGAに実装し、これに対応したゲームとコントロールソフトを実行して動作検証してみたいと思います。

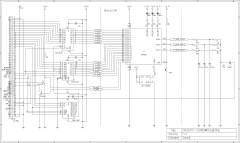

今回は、雑誌に掲載されている回路のブロック図と前回の回路図があるのでFPGA周りの回路だけを設計します。FPGA内部の実装としては、

- サウンド機能(PSG部分)

前回と同じだが、PSG内の音量バランスは少し調整した。

- パラレルI/O(VIA部分)

PIAに代わってVIAが使われているが、データをラッチする動作は前回と同じ。

- タイマ機能(VIA部分)

今回、新たに実装する部分。一定期間ごとにIRQ割り込みを発生させる。

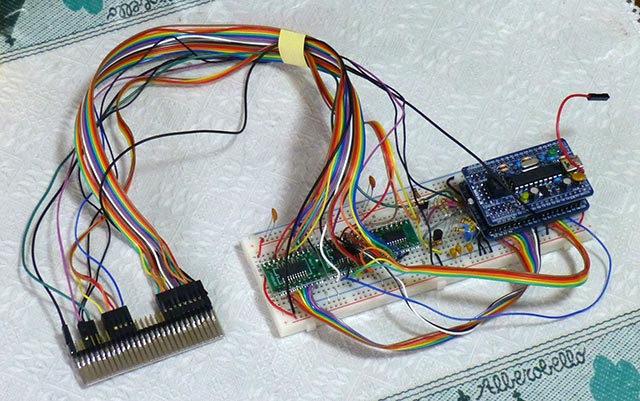

音声出力はPSG3つ分、3本をそれぞれRC回路(ローパスフィルタ)でアナログ信号にしてマーク5のSOUND INに送ります。今回は使用する信号線が多く、汎用ロジックICのピンが足りないので、RES信号とIRQ信号はトランジスタで実装することにしました。

実装が完了したらマーク5に接続するための回路をブレッドボード上に配線していきます。見た目は前回とほぼ同じですね。

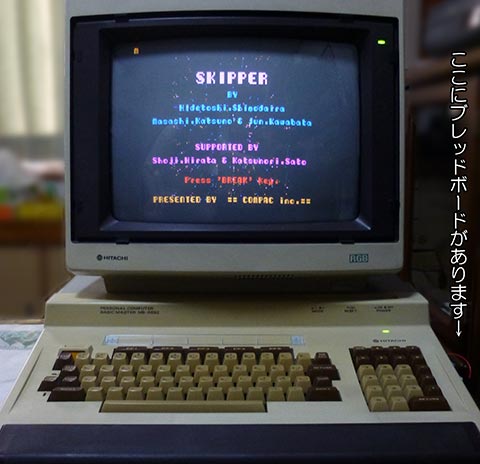

マーク5本体の背面からコードを通して接続し一通り確認したら電源を入れます。無事起動しましたので、PSGに対応したゲーム「スキッパー」をLOAD&RUNしてみます。お、音がなりました。このゲームはVIAのタイマー機能を使っていないのであっさり動いた模様です。ただ、音のなり方がエミュレータとは微妙に異なるようです。これはどちらが正しいのか…。

お次はVIAのタイマ機能を使用する9声PSGの「コントロールソフト」をLOAD&RUNしてみましょう。結果は…あああ、テンポが異常な速さで超早送りで再生されてしまう…。ここからは毎度おなじみのロジアナを使っての信号解析です。その結果、タイマーが機能していないのかIRQ割り込みが大量に発生している模様です。

どうやら、E信号のエッジ部分でタイマーのカウントダウンを行っているのが問題のようです。エッジ部分は信号が不安定になることがあるので、カウントダウンするタイミングを遅らせる必要がありました。同様に、データのラッチもエッジ部分からすこし遅れて行うようにしました。これらを直して再度実行すると、今度はうまく演奏を始めました…と思ったら止まってしまった。今度はタイミングを遅らせすぎて割り込み処理が呼ばれなくなったようです。再度タイミングを調整して……やっと最後まで演奏されました。ちょっと音質が悪いのは何だろう…アナログ回路かなぁ…。

まとめ

今回はエッジ部分での信号が不安定で、データのラッチや割り込み信号を出すタイミングで悩む結果となりました。このあたりはタイミング解析やシミュレーションを詳細にしないといけないということでしょうか。あと、音質が悪いのはアナログ回路に問題があるような気がしますがこの調査はまたの機会にします。(おわり)

ソースコード・ダウンロード

l3psg9_010_source.zip (93KB)

[MD5:316984d0be9bf4e73527c310953ce2c5]

※試される方は自己責任でお願いします。

◆関連ページ◆